本坛的《怎样才能用板载调试器来调试织女星开发板的RISC-V核》帖子中提到:

……我们没有把FreeLink的JTAG信号直接连到RV32M1的JTAG调试接口上……需要这里描述的飞线修改……

要使用FreeLink调试RISC-V核,只需要将FreeLink的JTGA信号连接到RISC-V核的JTAG调试连接头(J17)就可以了。(具体略)

这个飞线修改一般的步骤是:

- 准备一块 JTAG 转接板,必须支持 1.27mm 10P 转 2.54mm (淘宝很多)

- 使用 1.27mm 10P 排线将 J17 连接到转接板

- 再小心地使用 2.54mm 杜邦线,从转接板的 2.54mm 连接器连接到开发板

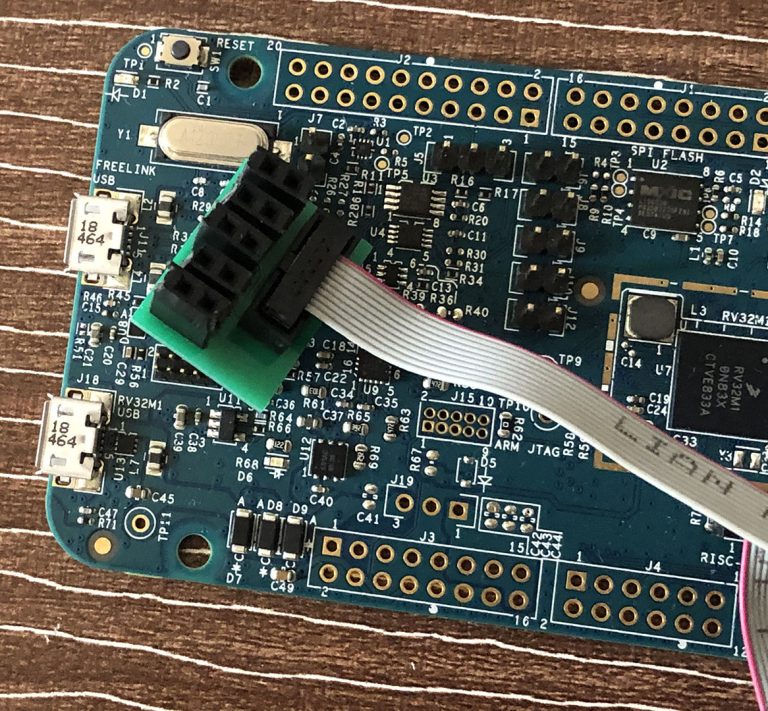

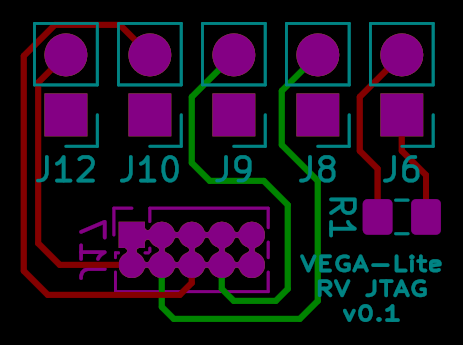

这样做繁琐易错,并且反复插拔很不方便。所以我设计了一个转接小板,用于扣在 J8/J9/J10/J12 之上,将其整体转换为一个 1.27mm 10P 的接口。这样就可以仅用一条 1.27mm 排线与 J17 进行方便的连接。效果如图:

这个转接板在 GitHub 开源,请访问 shamiao/vega-lite_riscv_jtag_conn_board。这是一个很小的项目,没有什么重大价值,请随意取用。

原创帖子,最早发表于我个人博客的《Rust+RV32M1:开发环境设置》,摘编转贴到本论坛。

预告:Rust语言开发RV32M1平台(创意竞赛参赛项目)的内容也将迅速转贴上来。